# Contents

| Introduction 1 |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                       |                                        |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|

| 1              | <b>Ran</b><br>1.1<br>1.2                                                                                                        | Adom Number Generators FoundationsRandom Number Generators ClassificationTRNG General Scheme1.2.1Where is Randomness? Entropy Source (ES)1.2.2Entropy Harvester (EH)1.2.3Digital Post-Processing1.2.4TRNG Figures of merit & Tradeoffs                                                                                                                                | <b>3</b><br>3<br>5<br>5<br>6<br>6<br>9 |  |  |

| 2              | <ul> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> <li>2.9</li> </ul> | adomness ToolboxThermal Noise (Johnson-Nyquist noise)Fourier TransformProbability theoryQuantizationQuantizationStochastic Process (SP)2.5.1 SP Characterization2.5.2 SP StationarityGaussianity2.6.1 Jointly Gaussian Vector (JGV)2.6.2 Additive White Gaussian Noise SP (AWGN)EntropyHamming DistanceLimit Behavior of RVsPearson's Chi-Squared test ( $P\chi^2t$ ) | 22                                     |  |  |

| 3              | <b>Arc</b><br>3.1                                                                                                               | hitecture & Design of RNGAnalog Chaotic ADC3.1.1 Pipeline ADC Converter3.1.2 Modified Single ADC Cell3.1.3 Chaotic ADC Pipeline3.1.4 Chaotic ADC SummaryDigital Metastable Power-Up SRAM3.2.1 Static Random Access Memory (SRAM) Circuit3.2.2 Skews of SRAM cells3.2.3 FERNS method: SRAM fingerprints                                                                | 35                                     |  |  |

|   |      | 3.2.4          | TRNG in SRAM                                                                   |   |   |     | 42       |

|---|------|----------------|--------------------------------------------------------------------------------|---|---|-----|----------|

|   |      | 3.2.5          | Metastable SRAM Summary                                                        |   |   |     | 44       |

|   | 3.3  | Intel®         | Ivy Bridge Core <sup>TM</sup> Bull Mountain DRNG $\ldots$                      |   |   |     | 44       |

|   |      | 3.3.1          | Intel Bull Mountain DRNG                                                       |   |   |     | 44       |

|   |      | 3.3.2          | ES and Health and Swellness Tests                                              |   |   |     | 45       |

|   |      | 3.3.3          | DRBG: AES CBC-MAC                                                              |   |   |     | 47       |

|   |      | 3.3.4          | BIST and Operating Modes                                                       |   |   |     | 49       |

|   |      | 3.3.5          | Intel Bull Mountain Summary                                                    |   |   |     | 50       |

|   | 3.4  | Two C          | Open Source TRNG                                                               |   |   |     | 50       |

|   |      | 3.4.1          | HotBits                                                                        |   |   |     | 50       |

|   |      | 3.4.2          | $LavaRnd^{TM}$                                                                 |   |   |     | 51       |

|   | 3.5  | PRNG           |                                                                                |   |   |     | 51       |

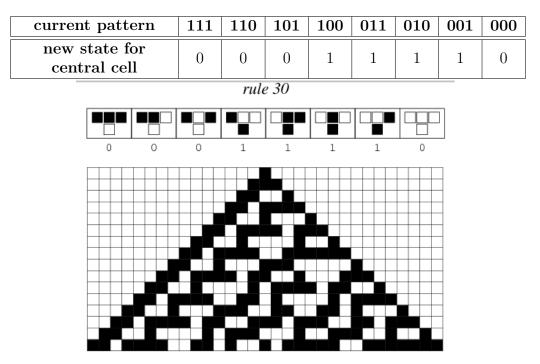

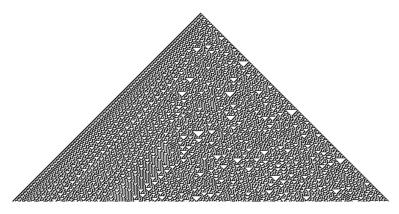

|   |      | 3.5.1          | Wolfram's Rule 30                                                              |   | • |     | 51       |

| 4 | The  | oretica        | I Analysis of RNG                                                              |   |   |     | 55       |

|   | 4.1  | Analog         | g Markov Chaotic sources and Pipeline ADCs                                     |   |   |     | 55       |

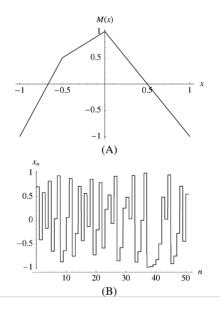

|   |      | 4.1.1          | Discrete-Time Chaotic Model                                                    |   |   |     | 55       |

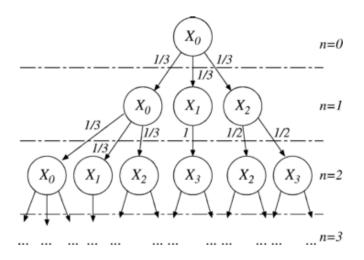

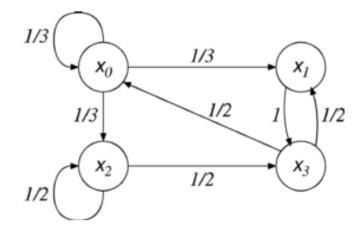

|   |      | 4.1.2          | Markov Chain characterization                                                  |   |   |     | 56       |

|   |      | 4.1.3          | Ideal chaotic map: Bernoulli Shift                                             |   |   |     | 58       |

|   |      | 4.1.4          | Chaotic Model for ADC Pipeline                                                 |   |   |     | 60       |

|   | 4.2  | 0              | l Metastable Power-Up SRAM                                                     |   |   |     | 62       |

|   |      | 4.2.1          | Guessing Probability and Min-Entropy                                           |   |   |     | 62       |

|   |      | 4.2.2          | Supply Voltage and Static Noise Margin (SNM)                                   |   |   |     | 63       |

|   |      | 4.2.3          | Negative Bias Temperature Instability (NBTI)                                   |   |   |     | 65       |

|   | 4.3  |                | eneration Intel <sup>®</sup> Core <sup>TM</sup> family processor Ivy Bridge Di | 0 |   |     |          |

|   |      | 4.3.1          | Metastable ES                                                                  |   |   |     | 66       |

|   |      | 4.3.2          | ES Failure Modes                                                               |   |   |     | 67       |

|   |      | 4.3.3          | DPP and Clock Gating                                                           |   | • |     | 69       |

| 5 | Test | 0              | a RNG                                                                          |   |   |     | 71       |

|   | 5.1  |                | ical Fails                                                                     |   |   |     |          |

|   |      | 5.1.1          | Cracking Data Encryption Standard (DES)                                        |   |   |     | 71       |

|   | •    | 5.1.2          | OpenSSL DSA and ECDSA                                                          |   |   |     | 72       |

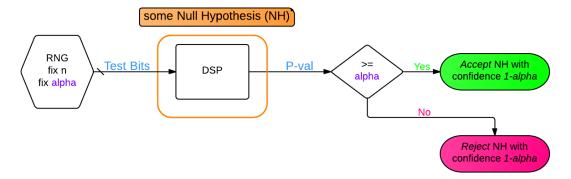

|   | 5.2  |                | Statistical Hypothesis Testing (SHT)                                           |   |   |     | 73       |

|   | 5.3  |                | test suite: $SP800-22$                                                         |   |   |     | 75       |

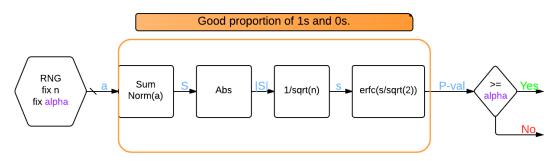

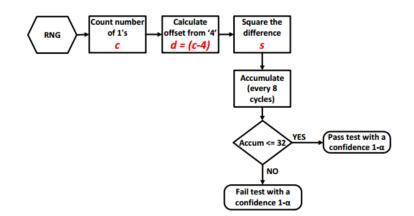

|   |      | 5.3.1          | Frequency Mono-bit (FMT)                                                       |   |   |     | 78<br>70 |

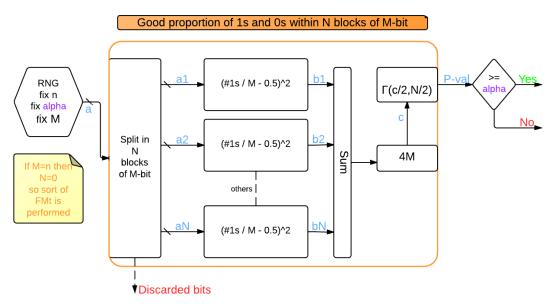

|   |      | 5.3.2          | Frequency Test within a Block (FTwB)                                           |   |   |     | 79<br>70 |

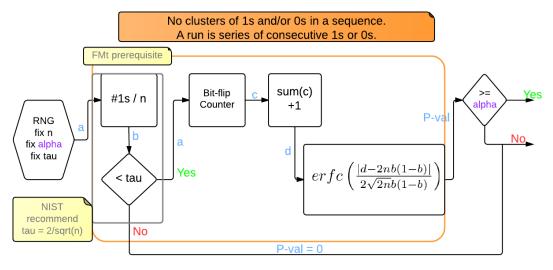

|   |      | 5.3.3<br>5.2.4 | Runs Test (RT)                                                                 |   |   |     | 79<br>81 |

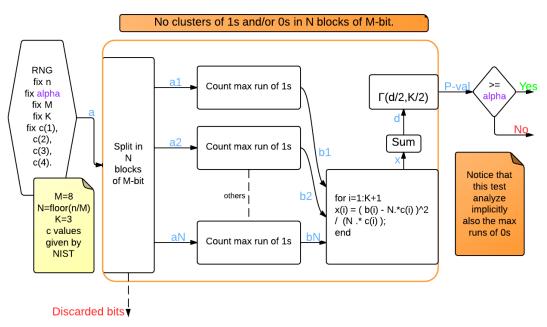

|   |      | 5.3.4<br>5.2.5 | Longest Run of 1s Test (LR1sT)                                                 |   |   |     | 81<br>81 |

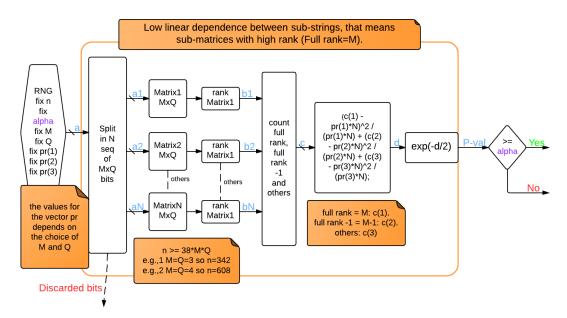

|   |      | 5.3.5<br>5.2.6 | Binary Matrix Rank Test (BMRT)                                                 |   |   |     | 81<br>82 |

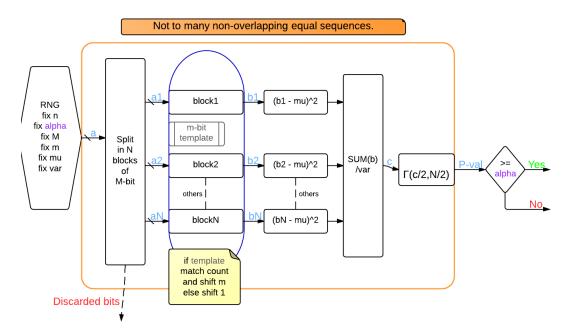

|   |      | 5.3.6          | Non-overlapping Template Matching Test (NoTMT)                                 |   |   |     | 83<br>84 |

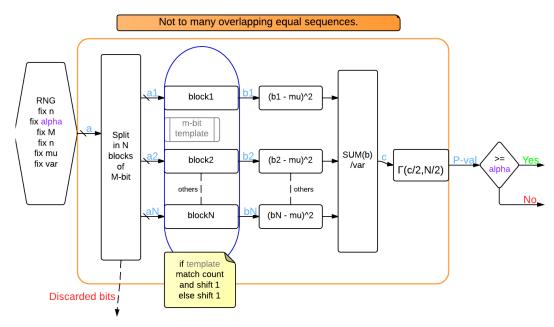

|   |      | 5.3.7<br>5.3.8 | Overlapping Template Matching Test (OTMT)                                      |   |   |     | 84<br>85 |

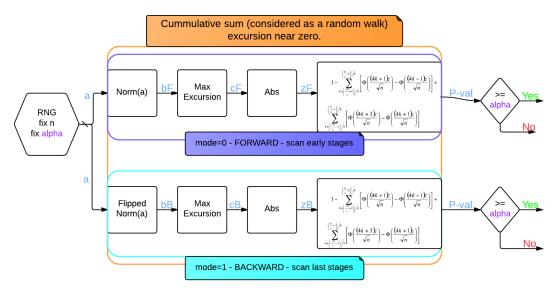

|   |      | 5.3.8          | Cummulative Sum Test (CST)                                                     |   | · | • • | 00       |

| 6   | Hare             | dware Implementation of Reduced NIST SP800-22         | 87  |  |  |  |

|-----|------------------|-------------------------------------------------------|-----|--|--|--|

|     | 6.1              | Abstract                                              | 87  |  |  |  |

|     | 6.2              | Motivations                                           | 88  |  |  |  |

|     | 6.3              | Reduced NIST SP800-22 test suite                      | 89  |  |  |  |

|     | 6.4              | Lightweight Implementation of reduced NIST Test Suite | 91  |  |  |  |

|     | 6.5              | MATLAB Code                                           | 93  |  |  |  |

|     |                  | 6.5.1 Input Functions                                 | 94  |  |  |  |

|     |                  | 6.5.2 Output Scripts                                  | 96  |  |  |  |

|     | 6.6              | Logic Implementation and Results                      | 113 |  |  |  |

|     | 6.7              | Conclusions and Future Work                           | 115 |  |  |  |

| Co  | onclus           | sions                                                 | 117 |  |  |  |

| Lis | st of            | Figures, Tables and Algorithms                        | 120 |  |  |  |

| Bi  | Bibliography 125 |                                                       |     |  |  |  |

| No  | Iomenclature 129 |                                                       |     |  |  |  |

# Introduction

The **privacy** is a fundamental right of each person and it's put to big test in this technological era, thus it is important to understand how to protect our information from being (ab)used or altered.

Random Number Generators (RNGs), are essential components for every *crypto-graphic* system and application [2]. They can be used for the generation of random session keys, signature keys and signature parameters, challenges and zero knowledge proofs and nonces. Wrong and poor implementation of these modules is a risk that cannot be accepted when we spoke about *security* and *integrity* of precious information. In addition, RNGs can be used, not only for cryptographic application but also for *stochastic simulation*, such as Monte Carlo methods, used to solve problems heuristically, because their intrinsic complexity does not permit to solve them analytically. Consider as an example, the optimal distribution of service times in complex multi-user system or the study of the correlated and uncorrelated variation in analog and digital ICs.

An ideal RNG is capable of generate *ideal secrets*, namely aperiodic, non deterministic bit sequence, thus the random bit produced are independent and uniformly distributed over a certain range. A perfect RNG, however, is a *fiction* [28]. In this work I will focus my attention on the best feasible approximation of an ideal RNG, defined as **True Random Number Generator (TRNG)**. This module is the basic primitive to build of every crypto-system. It is mandatory also in the Pseudo Random (Algorithmic) world. Their realization exploits specific *non-deterministic* physical phenomena from various branch of physics.

To face this challenging problems I will show a strong mathematical model, from which I will deduce a collection of statistical tools, like Fourier transformation, Entropy and Hamming distance. Without these instruments it is not possible to analyze a RNG and quantify how much randomness there is in a given bit sequence. Remember that randomness is a *relative* subject.

I will explore "ad hoc" methodologies for design RNG: analog and digital solutions. In the specific context of cryptography, one can be faced with a malicious person, defined as an **attacker** who does not only has knowledge of the RNG's design and the possibility to analyze its outputs, but also he can try to affect or control the RNG. So, for a designer it is not sufficient to have a theoretical abstraction of a RNG in mind, but also its concrete realization and its possible flaws in the design process, e.g. side-channel attack immunity, tamper resistance.

In the past, a lot of research work has been devoted to the development of good physical random sources and a variety of design have been proposed. Less work has been spent in the development of suitable *tests* and assessment criteria. Thus I will explore this filed and present the theoretical foundations, defined as Statistical Hypothesis Testing (SHT) and I will introduce some test suite: NIST SP800-22, DIEHARD, dieharder.

Finally I will propose the core of this work: the design and the implementation of a CMOS on-chip test module. This circuit is able to perform some tests using only some combinatorial logic, counters and comparators (full hardware implementation) and return some results to check on-line the health of the target RNG.

# 1 Random Number Generators Foundations

## 1.1 Random Number Generators Classification

In cryptographic/security applications the random number generation mechanism falls into two classes:

- 1. True Random Number Generators (TRNG) OR Physical Random Number Generators (PhRNG): exploit Non-Deterministic events and return aperiodic sequences;

- 2. Pseudo Random Number Generators (PRNG) OR Deterministic Random Bit Generator (DRBG): exploit Deterministic events and return periodic sequences;

The first class of RNG is formed by True or Physical RNG. True Random Number Generators harness random physical phenomena to generate random bits. On-chip noise, clock jitter and stray electromagnetic field are some of the sources of randomness for a TRNG. TRNG circuits are often used to periodically seed a PRNG, generate nonces for security protocols and in data encryption/decryption. The most commonly used TRNG circuits are based on Ring Oscillators which sample and digitize on-chip jitter noise to generate random bits. Ring Oscillator based circuits are also popular for FPGA based implementations. Noise amplifiers and Analogto-Digital Converters (ADC) are used to sample on-chip thermal and shot noise to obtain random samples. Digital circuits for sampling thermal noise use metastable elements like a pair of cross coupled inverters. Power up state of SRAM, read-refresh collision in DRAM and Random Telegraph Noise (RTN) in Contact Resistive RAM [12] are examples of memory-cell based TRNG circuits.

Another example of first class random number generation, not detailed in this work, is what is called, not strictly physical, hence true RNG, and it is based on the intersection of casual chains, remember that the combination of events of several process which are independent of each other may behave completely randomly. Consider, as an example, computer data as time of interrupts, hard-disk seek times or user interactions, like mouse movement or keystroke timings. The intersection of these data can provide a source of randomness. Modern UNIX and Windows Operating System s have OS-level RNGs based on the timing of kernel IO events. Unfortunately, the quality of the entropy collected depends upon the system's configuration and hardware. For example the entropy available from an embedded device without hard drive or keyboard, such as a smartphone, may be insufficient for security application, so it is better to rely on, first class, True RNG.

The second class is formed by *Pseudo* Random Number Generator or *Determinis*tic Random Bit Generator, denoted in this work as **PRNG** and **DRBG**.<sup>1</sup> A PRNG uses deterministic processes, in the specific finite memory algorithms, to generate a *periodic* series of output from an initial *seed* and a *current state*. Because the output is purely a function (e.g., bijection) of the seed data, the unpredictability of the output can never exceed the unpredictability of the seed. Given the same seed, a PRNG will always output the same sequence of values so the possibility of retrieving information about the seed through the observation of output sub-sequences and their repeatable behavior can hardly be desirable in applications such as data security and cryptography. It can, however, be computationally infeasible to distinguish a well-seeded DRBG from an ideal RNG because often it is possible to extend the period with regard to the time scales on which a piece of equipment is employed. The substantial advantage of this class with respect to the first is the *algorithmic* nature, which makes them easily embeddable in any digital circuit or system, instead TRNG often requires dedicated hardware that is difficult to embed. It is important to focus the attention on the seed that by definition requires true random numbers, so even in this case a TRNG unit is required somewhere and it is fundamental for the system.

Chronologically speaking the first two class of RNGs represented the starting point of the design methodologies and so in a certain sense a "classic" scheme. But in the recent years novel methodologies merges the two classes in what can be defined as an **hybrid** RNG. This architecture use both components taking advantage of the best parts of each, e.g., super-secure true random number for the seed, fast and embeddable algorithm for hashing the outputs. In fact re-seeding a DRBG very frequently and with fresh true random number can lead to very good performance, an example will be showed in sec. 3.3. This novel design approach can be classified with the term **Cryptographically Secure Pseudo Random Number Generator** (**CSPRNG**) and by definition is a RNG capable to pass all statistical tests that run in *polynomial* time asymptotically. All such polynomial time statistical tests, called also *efficient* statistical tests, will be unable to distinguish a CSPRNG from a true random source.

It is important, for the scope of this work, to define a reference RNG that is defined as an **ideal** RNG. This mathematical construction is capable to generate infinitely long sequence formed by random numbers that are *uniformly (identically) distributed* in their range, for digital circuit the interval is simply[0, 1], and *independent* from each other so it can produce unguessable, uncorrelated random output (for the statistics behind that see sec. 2.5). Starting from this model it is possible to analyze which kind of feasible architecture, during normal operation, cannot be distinguished

<sup>&</sup>lt;sup>1</sup>Notice that, in this case the difference between the word *number* and the word *bit* does not exist because all the applications concern with random numbers generated from digital circuits outputs, that are bits.

from a perfect RNG. This is the fundamental sentence! TRNGs will be the core of this work, because they represent the *best* feasible approximation of an ideal RNG and a fundamental *primitive* for all security-related application.

# 1.2 TRNG General Scheme

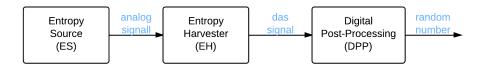

The most synthetic, high level block scheme of a True Random Number Generator is in Fig. 1.1.

Figure 1.1: Basic high-level block scheme of TRNG.

This is a comfortable abstraction used recursively in this work.

## 1.2.1 Where is Randomness? Entropy Source (ES)

Design and Analysis of an Random Number Generator is based on the *understanding* of randomness [28]. Firstly it is needed to *find* randomness, common example of what is defined as an **Entropy Source (ES)** can be:

- ► Thermal (Johnson-Nyquist) noise: spontaneous voltage fluctuations in a (semi) conductor in thermodynamic equilibrium, that result from the thermal agitation of the electric charges (carriers) in the material of the (semi) conductor. [23, 15];

- ▶ Schottky (Shot) noise, which describes the randomness in a current as it begins to flows through a conductor e.g., from a Zener diode [29];

- ▶ Time between emissions of radioactive decays;

- ► Brownian motion [4];

- ▶ Quantum photon effect;

All these examples are physical random micro-cosmic process, defined by their nature, as **Non Deterministic**. The word *entropy* has a central meaning because quantify the amount of randomness present in a sequence, its formal definition will be presented in sec. 2.7. This quantity can be extracted in many ways depending on the type of ES, common examples are chaos on deterministic analog signals sec. 3.1, power-up state of memory cells sec. 3.2, meta-stability of devices sec. 3.3 or random clock jitter samples.

It is possible to model these random sources as a time-continuous analog signal generators. The signals then can be *digitized* after uniform time intervals (e.g., using a comparator). These samples are defined as *digitized analog signal*, briefly denoted as *das random numbers* or as *raw bits*. Such generators are called True or Physical RNGs, denoted in this work as True Random Number Generators (TRNGs) or Physical Random Number Generators (PhRNGs) and they are capable to produce *aperiodic, uncorrelated* random outputs.

## 1.2.2 Entropy Harvester (EH)

The Entropy Harvesting stage is the part of the circuit devoted to the extraction of random bit. The first and most common example of EH circuit is the comparator, that returns some constant voltage value if the input fall in a certain thresholds interval. There are also examples in which the EH stage is embedded in the ES:

- 1. Chaos in a pipeline ADC circuit sec. 3.1;

- 2. Metastability in SRAM power-up state sec. 3.2;

### 1.2.3 Digital Post-Processing

Usually the das random number are algorithmically post-processed in order to reduce, more precisely to mask potential weakness of the ES e.g., bias. The outputs of this stage, denoted as Digital Post-Processing (DPP) stage, are called *internal* random numbers. Upon external call the same outputs are usually called *external* random numbers.

There are many ways to post-process a bit sequence, the common tradeoff in digital circuit design is between area/power consumption and strength of the algorithm. The DPP stage always increase the entropy of the system, reducing its throughput (bit-rate) [33]. I briefly present four solutions in ascending order of complexity.

#### 1.2.3.1 XOR Filter

The XOR function is a very common entropy extractor used also in sec. 3.1.

| Α | В | $\mathbf{A}\dot{\vee}\mathbf{B}$ |

|---|---|----------------------------------|

| 0 | 0 | 0                                |

| 0 | 1 | 1                                |

| 1 | 0 | 1                                |

| 1 | 1 | 0                                |

Table 1.1: XOR Function table of truth.

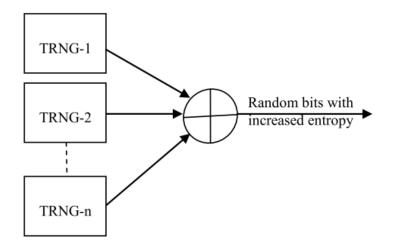

Outputs of two or more TRNG circuits XORed (bit wise added) to improve the entropy of the output as shown in Fig. 1.2. Bias in one of the circuits is masked by the other TRNG circuits.

Figure 1.2: XOR Filter.

This technique also provides tolerance against device wear out or side channel attacks. Although the XOR function provides a simple implementation for improving the entropy of the design, it leads to overhead due to need for multiple TRNG circuits.

#### 1.2.3.2 von Neumann corrector

In 1951, JOHN VON NEUMANN presented a method for removing all 0/1 bias from a RNG. This method, successively defined as *the von Neumann corrector* produces a balanced distribution of ones and zeros. As can be seen from Tab. 1.2, the function converts bit pairs [0,1] from the TRNG into an output 1 bit and the pairs [1,0] into an output bit 0. The pairs of bits [0,0] and [1,1] are discarded.

| Input bit pair | Output bit |  |  |

|----------------|------------|--|--|

| 0 0            | discard    |  |  |

| 0 1            | 1          |  |  |

| 1 0            | 0          |  |  |

| 11             | discard    |  |  |

Table 1.2: von Neumann corrector.

The Von Neumann corrector is very efficient in terms of producing an equal distribution of 1s and 0s. But, since the output rate of the Von Neumann corrector is not constant, the generated bits need to be stored, (e.g., in a shift register) before using for further processing. Even with very high entropy TRNG, the maximum bit rate achievable is half the bit rate of the TRNG.

#### 1.2.3.3 Secure Hash Algorithm (SHA)

Secure Hash Algorithms are four cryptographic functions distinguished chronologically as: SHA-0, SHA-1, SHA-2, SHA-3. A long explanation is out the scope of this work. Basically a long bit sequence is processed by a complex non-linear function, defined as *compression function*. The hashing process is repeated many times, each *round* the compression function change slightly. The output produced is called *digest* because it is always a reduction of the provided input, notice that even if the complexity of the functions very high, the algorithm is still *invertible* (pseudo-randomness).

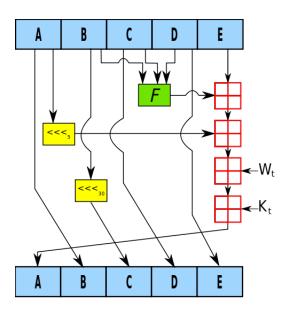

SHA-1 (1995) is the most widely used hash function of the recent years. Each round is described in Fig. 1.3.

Figure 1.3: SHA-1 round.

A B C D and E are 32-bit sequence, F is the compression function that varies each round,  $\ll_n$  is the left-bit rotation by *n* places operator, *n* varies each operation.  $W_t$  and  $K_t$  are respectively the expanded message word and the constant of round t.  $\boxplus$  denotes addition modulo  $2^{32}$ .

After 80 rounds a 160-bit digest output is produced.

AES posso anche non metterlo

### 1.2.4 TRNG Figures of merit & Tradeoffs

As a summary for the end of this chapter, are presented in Tab. 1.3 the usual *tradeoffs* for the design and testing of a TRNG circuit. Notice that, the *classical* metric, namely: power, area and throughput, are not sufficient to classify a TRNG IC, there is the need of additional variable that quantifies the security and the level of randomness of the circuit.

| Left                         | Right                      |

|------------------------------|----------------------------|

| Area /Power Consumption      | Bit Entropy                |

| ES Complexity                | DPP Complexity             |

| Testability /Tamper          | Embeddability /Reusability |

| Resistance                   |                            |

| Mixed Circuit                | Fully Digital circuit      |

| Throughput /Bandwidth        | Hardw /Softw complexity    |

| /Entropy Rate                |                            |

| Specification /Certification | Dedicated Hardware /Cost   |

| Technology Scaling           | Process Variation          |

| ASIC Implementation          | FPGA implementation        |

| (Re)Configurability          | Application Dependence     |

Table 1.3: TRNG circuit tradeoffs.

# 2 Randomness Toolbox

## 2.1 Thermal Noise (Johnson–Nyquist noise)

WALTER SCHOTTKY first postulated the existence of **thermal noise** and **shot noise** in 1918 but J. B. JOHNSON discover and measure it. This in an extract that came from [15]:

"Ordinary electric conductors are sources of spontaneous fluctuations of voltage which can be measured with sufficiently sensitive instruments. This property of conductors appears to be the result of thermal agitation of the electric charges in the material of the conductor.

The effect has been observed and measured for various conductors, in the form of resistance units, by means of a vacuum tube amplifier terminated in a thermocouple. It manifests itself as a part of the phenomenon which is commonly called tube noise. The part of the effect originating in the resistance gives rise to a mean square voltage fluctuation V2 which is proportional to the value R of that resistance. The ratio V2/R is independent of the nature or shape of the conductor, being the same for resistances of metal wire, graphite, thin metallic films, films of drawing ink, and strong or weak electrolytes. It does, however, depend on temperature and is proportional to the absolute temperature of the resistance. This dependence on temperature demonstrates that the component of the noise which is proportional to R comes from the conductor and not from the vacuum tube..."

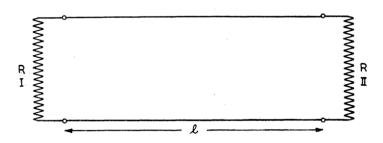

After Johnson's results, H. NYQUIST theoretically deduces the noise electromotive force (thermal noise) from thermodynamics and statistical mechanics [23]. He started from the point that the electromotive force due to thermal agitation in conductors is a universal function of *frequency*, *resistance* and *temperature* and of these variable only. Furthermore this statement is valid independently on the type of conductor e.g., silver, lead or electrolyte.

To determine the form of this function it can be convenient to consider two **ideal** conductors, each of resistance R, connected as showed in Fig. 2.1 by means of a non-dissipative transmission line. In order to avoid radiation one conductor may be internal to the other. The characteristic capacity C and impedance L per unit length of the line is modeled in order to obtain R as characteristic impedance. Under these conditions there are no reflection at either end of the line. Let the length of the line by l and the velocity of propagation v.

Figure 2.1: Resistive network thermal electromotive force.

After thermal equilibrium is established, let the absolute temperature of the system be T. There are now, due to the generated thermal electromotive force, two trains of energy traversing the line, one from left to right and viceversa.

At any instant after thermal equilibrium, let the line be *isolated* from the two conductors by application of a short-circuit at both ends. Now there are complete reflection at the two ends and the energy which was on the line at the time of isolation remains trapped. It is possible to model the line as *vibrating at its natural frequency*. The fundamental frequency is

$$\nu_0 = v/2l. \tag{2.1}$$

and it is quantized for an integer value i = 1, 2, 3, ..., n by the relation  $\nu_i = i\nu_0$ . Consider any  $\nu_i$  as a *mode* of vibration or as a *degree of freedom* of the system. Each degree of freedom has an average constant energy associated equal to:

$$E_{thermal} = k_B T. (2.2)$$

where  $k_B$  is the Boltzmann constant. Half of  $E_{thermal}$  is magnetic and half is electric. The total energy of the vibrations within a generic frequency interval  $d\nu$  is:  $(2lk_BT/v) d\nu$ .

But since there is no reflection in the Fig. 2.1 configuration, this is the energy within that frequency interval that the two conductors transferred to the line during the time of transit l/v and the average power within that frequency interval transferred by the two conductors to the line during the same time interval is  $k_B T d\nu$ .

Using basic formulas of circuit theory, I = E/2R  $P = RI^2$ , that link current, voltage and power of a conductor is possible to write the square-root of the thermal electromotive force in a conductor of pure resistance R and temperature T, see Eq. 2.3:

$$E_{\nu}^2 \,\mathrm{d}\nu = 4Rk_B T \,\mathrm{d}\nu. \tag{2.3}$$

This expression can be extended for any other network build up of *impedance*  $Z_{\nu}$  members at temperature T:

$$Z_{\nu} = R_{\nu} + iX_{\nu} = 1/Y_{\nu}.$$

$$E^2 \,\mathrm{d}\nu = 4R_\nu k_B T \,\mathrm{d}\nu. \tag{2.4}$$

Let  $Y(\omega)$  be the transfer *admittance* of any network from the member in which electromotive force is generated to the member in which the resulting current is measured. Let  $I\omega = 2\pi\nu$  and let  $R(\omega) = R_{\nu}$  be the resistance of the member in which the electromotive force is generated. The squared value of the current measured within the interval  $d\nu$  is :

$$I^{2} d\nu = E_{\nu}^{2} |Y(\omega)|^{2} d\nu = (2/\pi) k_{B} T R(\omega) |Y(\omega)|^{2} d\omega.$$

Integrating from 0 to  $\infty$

$$I^{2} = (2/\pi) k_{B}T \int_{0}^{\infty} R(\omega) |Y(\omega)|^{2} d\omega.$$

(2.5)

Eq. 2.5 is the same formula obtained in Johnson's paper, confirming Nyquist theoretical proof.

Quantities such *charge*, *number* and *mass* of the carriers of electricity do not appear explicitly in the formula, therefore they enter indirectly because they influence the value of  $R_{\nu}$ .

Notice that electromotive force in engineer typical language is know as *one-sided* power spectral density, or voltage variance (mean square) per hertz of bandwidth denoted as:

$$\overline{v_n^2} = 4k_B T R \Delta f. \tag{2.6}$$

The thermal (Johnson-Nyquist) noise in is ideal approximation is defined as **white** noise for reason that will be clear in sec. 2.6.2 with its statistical description. Notice that the noise's color classification includes also *pink*, *red* (*Brownian*), *purple* and *gray*. In addition pink noise is often defined as *flicker* noise or 1/f noise.

There are two theorems that can be used for thermal noise analysis in *thermal* equilibrium. The first one derives from the **Parseval's theorem** and states that:

**Theorem 2.1.** The noise mean power is equal to the integral of the Power Spectral Density (PSD) of noise at thermal equilibrium, see Eq. 2.6, over all the frequencies.

The second one is more powerful because simplify computations in complex systems, and it is called **equipartition theorem** and it comes from statistical mechanics. It states that:

**Theorem 2.2.** Any energy storage elements (also called "degree of freedom"), such as inductor or capacitor, in thermal equilibrium holds an average noise energy of kT/2.

As an example, using the equipartition theorem, it can be easily computed the noise mean power of an RC network without any integral. The only energy storage element (degree of freedom) in this case is the capacitor, recalling that the mean energy is  $E = \frac{1}{2}VQ$ , and the capacitance is defined as C = Q/V, it is easy to see that the average noise energy is:

$$\frac{1}{2}CV^2 = \frac{kT}{2}.$$

(2.7)

thus the noise mean power is:

$$V^2 = \frac{kT}{C}.\tag{2.8}$$

Notice that, for this circuit, the noise mean power does *not* depend on the value of the resistance R. This result is not valid in all situation, in particular for more complex circuit where they must be introduced *parasitic* capacitance that can lead to a noticeable degradation in noise performance. A common example is Switched Capacitors circuits that implement Track-and-Hold function used for filters, data converters (A/D and D/A), sensor interfaces and dc-dc converters.

Noise mean power and noise Power Spectral Density (also called Power Density Spectrum PDS) are fundamental quantities for engineering applications, their computations involve statistics that helps to map randomness into a measurable set, see sec. 2.5 for more details. In the specific, noise analysis it is a matter of hypothesis and abstractions, it uses sampling technique as explained in sec. 2.4, lumped circuit elements to model noise sources, Channel (Network) Transfer Functions (CTFs) to model input-output relations over frequency and discrete-time domains to model clocked circuits.

### 2.2 Fourier Transform

**Definition 2.1.** For continuous variable, given any integrable function  $f : \mathbb{R} \to \mathbb{C}$ , can be defined a transformation  $\mathcal{F} : \mathbb{R} \to \mathbb{C}$  such that

$$\mathcal{F}[f(y)] = \hat{f}(x) = \int_{-\infty}^{+\infty} f(y)e^{-2\pi ixy} \,\mathrm{d}y.$$

(2.9)

when exists the inverse it has the form:

$$\mathcal{F}^{-1}\left[\hat{f}(x)\right] = f(y) = \int_{-\infty}^{+\infty} \hat{f}(x)e^{2\pi ixy} \,\mathrm{d}x.$$

(2.10)

**Definition 2.2.** For **discrete** variable, given a function  $x_n : x[n]$  with n = 0, 1, 2, ..., N-1, can be defined its Discrete Fourier Transform (DFT) as:

$$\mathcal{F}[x[n]] = X(k) = \sum_{n=0}^{N-1} x[n] e^{\frac{-2\pi i}{N}kn}.$$

(2.11)

As before if exists the Inverse Discrete Fourier Transform (IDFT) and it has the form:

$$\mathcal{F}^{-1}[X(k)] = x[n] = \frac{1}{N} \sum_{k=0}^{N-1} X_k e^{\frac{2\pi i}{N}kn}.$$

(2.12)

For any discrete time function g[n], that comes from the sampling of a continuous function g, sampled n times with period T, exists a precise relation between the Fourier transform of the discrete-value samples and the Fourier transform of the continuous sampled function:

$$G(\xi) = \frac{1}{T} \sum_{k=-\infty}^{+\infty} \hat{g}(\xi - \frac{k}{T}).$$

(2.13)

**Theorem 2.3.** so the DFT of the discrete-value samples  $G(\xi)$ , is equal to the periodic repetition 1/T of the Fourier Transform of the continuous sampled function  $\hat{g}(\xi)$ .

In both cases, the typical engineering application involves the relation between functions of time time measured in s and their transformation in the frequency domain, measured in  $s^{-1} = Hz$ .

# 2.3 Probability theory

All aspects that regards randomness, as TRNG, should be encoded in something usable, so a clear mathematical model is necessary. *Probability theory* is an attempt to accomplish this purpose.

**Definition 2.3.** Given  $\Omega$  as the set of all possible event and  $A \subseteq \Omega$  as a single event. Then it is useful to define a family of subsets of  $\Omega$  that satisfy certain properties, this subset is called  $\Sigma(\Omega)$  and it is a  $\sigma$ -algebra of  $\Omega$  Iff

- 1.  $A \in \Sigma(\Omega);$

- 2. if  $A \in \Sigma(\Omega)$  then  $\overline{A} = \Omega/A \in \Sigma(\Omega)$ ;

- 3. if  $A_j \in \Sigma(\Omega)$  then  $\bigcup_j A_j \in \Sigma(\Omega)$ ;

- a) applying *De Morgan's laws* can be noticed that 3. is valid also for intersection operation  $\cap$ .<sup>1</sup>

**Definition 2.4.** Given  $\Omega$  and one of its  $\sigma$ -algebra  $\Sigma(\Omega)$ , it is possible to define a *probability function* Pr such that:

${}^1\overline{A\cup B}\equiv\overline{A}\cap\overline{B}$  and  $\overline{A\cap B}\equiv\overline{A}\cup\overline{B}$

- 1.  $\Pr(\Omega) = 1;$

- 2. if  $A_j \cap A_k = \emptyset$  then  $\Pr\left(\bigcup_j A_j\right) = \sum_j \Pr(A)$ .

This function assumes value in the interval [01] and it is used as a fundamental metric (measure) to model random things.

**Definition 2.5.** Furthermore, can be defined a particular kind of  $\sigma$ -algebra called **Borel**  $\sigma$ -algebra on the set of  $\mathbb{R}$  numbers. It is represented with  $S_y$  and satisfies the following properties:

1.

$$S_y = \{x | x \le y\};$$

- 2.  $S_y \in \Sigma(\Omega);$

- 3.  $\Omega \in \mathbb{R}$ .

So  $S_y$  is the smallest  $\sigma$ -algebra in the set of  $\mathbb{R}$  numbers that contains all real intervals.

**Definition 2.6.** Borel  $\sigma$ -algebra can be used to define a *Random Variable (RV)* as a function  $x : \Omega \to \mathbb{R}^n$  such that:

$$if \quad A \in \Sigma(\Omega) \to x^{-1}(A) \in \Sigma(\Omega).$$

From this definition is possible to develop all the classic probability theory.

**Definition 2.7.** Given any RV x, it can be always defined its *Cumulative Distribu*tion Function (CDF), that is a function  $F_x : \mathbb{R}^n \to [0, 1]$

$$F_x(y) = \Pr\left(X \le y\right). \tag{2.14}$$

and its Probability Distribution Function (PDF), that is a function  $f_x : \mathbb{R}^n \to \mathbb{R}^+$

$$f_x(y) = \frac{\mathrm{d}}{\mathrm{d}y} F_x(y). \tag{2.15}$$

It is also valid the theorem of *Lebesgue*, valid for both discrete-value and continuous-value PDF, that states that:

**Theorem 2.4.** Given a continuous(discrete)-value RV x and its PDF and CDF. If you have a step in the PDF then put a  $\delta$ -function ( $\delta_{ij}$ -function) in the CDF.<sup>2</sup>

<sup>&</sup>lt;sup>2</sup>In the context of signal processing, the *Dirac* delta function ( $\delta$ ) is often referred to as the *unit impulse* symbol. Its discrete analog is the *Kronecker* delta function ( $\delta_{ij}$ ) which is usually defined on a finite domain and takes values 0 and 1.

Thus for a continuous-value RV x, and its CDF  $F_x$ . If  $f_x$  exists, is a non-negative Lebesgue-integrable function thus are valid the following relations:

$$F_x(y) = \int_{-\infty}^y f_x(\xi) \,\mathrm{d}\xi.$$

$$\Pr\left[a \le X \le b\right] = \int_a^b f_x(\xi) \,\mathrm{d}\xi$$

$$\int_{\infty} f_x = \int_{\infty} PDF = 1.$$

and for a discrete-value RV x, if  $f_x$  exists, are valid the following relations:

$$F_x(y) = \sum_{i=-\infty}^{j} f_x[i] = \sum_{i=-\infty}^{j} f_{x_i}.$$

$$\Pr\left[a \le X \le b\right] = \sum_{i=a}^{b} f_x[i].$$

$$\sum_i f_x[i] = \sum_i PDF = 1.$$

**Definition 2.8.** Another fundamental quantity is the *expectation* E, of a continuous(discrete) RV x, defined as:

$$\mathbf{E}\left[x\right] = \int_{-\infty}^{+\infty} x f_x(x) \,\mathrm{d}x. \tag{2.16}$$

$$\mathbf{E}\left[x\right] = \sum_{j}^{\infty} x_j f_{x_j}.$$

(2.17)

From this quantity can be extracted many statistical features of a RV, see Tab. 2.1:

| mean                                     | $\mu = \mathbf{m}_x = \mathbf{E}\left[x\right]$                                                  |

|------------------------------------------|--------------------------------------------------------------------------------------------------|

| variance                                 | $\sigma_x^2 = \mathbf{E}\left[ x - \mathbf{m}_x ^2\right] = \mathbf{E}[x^2] - (\mathbf{E}[x])^2$ |

| standard deviation                       | $\sigma_x = \sqrt{E[(x-\mu)^2]} = \sqrt{E[x^2] - (E[x])^2}.$                                     |

| $j^{th}$ order central moment            | $\mathbf{M}_x^j = \mathbf{E}[(x-\mu)^j]$                                                         |

| j <sup>th</sup> order non central moment | $\mathbf{m}_x^j = \mathbf{E}[x^j]$                                                               |

| j <sup>th</sup> order absolute moment    | $\mu_x^j = \mathbb{E}[ x ^j]$                                                                    |

**Table 2.1:** RV Statistical Features.

Given these quantities, there exists a theorem called *Chebishev's inequality*, useful to estimate a probability of a certain RV with unknown PDS, using only its mean and variance:

**Theorem 2.5.** Given a RV x, with finite mean  $\mu_x$  and finite variance  $\sigma_x^2$ , then for any real number k > 0,

$$0 \le \Pr(|x - \mu_x| \ge k\sigma_x) \le \frac{1}{k^2} \tag{2.18}$$

or equivalently

$$0 \le \Pr(|x - \mu_x| > k) \le \frac{\sigma_x^2}{k^2}.$$

(2.19)

**Definition 2.9.** There exists also a *Moment Generating Function* (MGF) of a RV that uses inverse Fourier transform, defined as:

$$\psi_x(\omega) = \mathcal{F}^{-1}[f_x](\omega) = \mathcal{F}[f_x](-\omega).$$

(2.20)

MGF has two important properties:

1. Can be expanded using Taylor series, this expansion serves to prove the Central Limit Theorem (CLT) see sec. 2.9:

$$\psi_x(\omega) = \sum_{j=0}^k m_x^j \frac{(2\pi i\omega)^j}{j!} + \mu_x^{k+1} \frac{|2\pi\omega|^{k+1}}{(k+1)!} \theta(\omega).$$

2. Deriving it k times and computing its value in 0, can be obtained the correspondent  $k^{th}$  order non central moment:

$$\frac{\mathrm{d}^k}{\mathrm{d}\omega^k}\,\psi_x(0) = (2\pi i)^k\,\mathrm{m}_x^k.$$

**Definition 2.10.** Given two RV  $x_0$  and  $x_1$ , is possible to define their *covariance* as:

$$\gamma_{x_0 x_1} = \mathbf{E} \left[ (x_0 - \mathbf{m}_{x_0})^* \left( x_1 - \mathbf{m}_{x_1} \right) \right].$$

(2.21)

The \* correspond to the complex conjugation operator or conjugate transposition of a matrix. Notice that, if  $x_0 = x_1 = x$ , then  $\gamma_{xx} = \sigma_x^2$ . Furthermore, if  $\gamma_{x_0x_1} = 0$ , then the two RV are *uncovariated*.

Finally given two RV  $x_0$  and  $x_1$ , it is possible to define their *joint PDF* also called *joint probability distribution*

$$f_{x_0x_1} = f_{x_0} \text{ and } f_{x_1}.$$

(2.22)

From this definition we can check one of the most important probability of RVs, their **independence**.

**Theorem 2.6.** Two or more RVs are independent if their joint PDF can be factorized into independent single PDFs.

$$f_{x_0,x_1,\dots,x_n}(y_0,y_1,\dots,y_n) = f_{x_0}(y_0)f_{x_1}(y_1)\dots f_{x_n}(y_n)$$

**Definition 2.11.** Given two RV  $x_0$  and  $x_1$ , is possible to define their *cross-correlation*:

$$\rho_{x_0 x_1} = \frac{\gamma_{x_0 x_1}}{\sigma_{x_0} \sigma_{x_1}}.$$

(2.23)

While the correlation of a random vector X is considered to be the correlation matrix (matrix of correlations). If  $x_o$  and  $x_1$  are two independent RVs with PDFs  $f_{x_0}$  and  $f_{x_1}$ , respectively, then  $f_{x_1-x_0}$  is formally given by the cross-correlation  $\rho_{x_0x_1}$ , it is also possible to compute the PDF of the sum of the two inverting the second RV.

There is a parallel theory of cross-correlation for *signal processing* application. In this case, cross-correlation is a measure of *similarity* of two waveforms. This is also known as a sliding dot product or sliding inner-product. For continuous functions, f and g, the cross-correlation is defined as:

$$(f \star g)(t) = \int_{-\infty}^{\infty} f^*(\tau) g(t+\tau) \,\mathrm{d}\tau.$$

where f \* denotes the complex conjugate of f. Similarly, for discrete functions, the cross-correlation is defined as:

$$(f \star g)[n] = \sum_{m=-\infty}^{\infty} f^*[m] g[n+m].$$

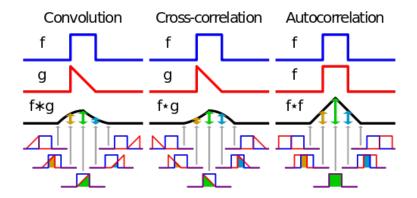

To compare these quantities see Fig. 2.2

Figure 2.2: Convolution, Cross-Correlation and Auto-correlation.

The cross-correlation is similar in nature to the convolution of two functions.

Notice that if two RVs are independent, then they are also uncovariated (and also uncorrelated), the inverse is true only for Gaussian(normal) RV, see sec. 2.6.

# 2.4 Quantization

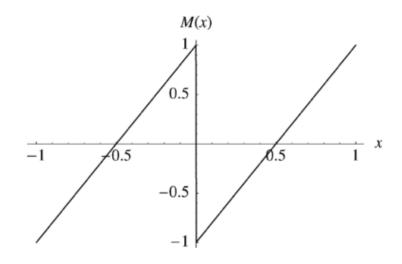

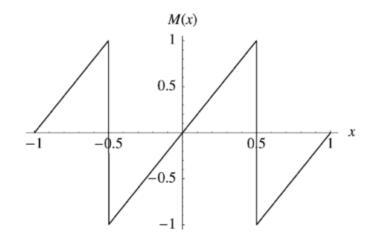

Every digital system presents a quantization circuit responsible of the translation of real-analog signal into processable-digital one. The aim of this circuit is to transform a continuous-time function, that can assume an infinite set of values into a discrete-time function, that can assume only a *finite* set of values. This operation is not reversible so it produces a loss of information, defined as *error of quantization*. Notice that, every circuit has a saturation point, so in real application the set of infinite values is bounded between two voltage/current values.

The mathematical model of the quantization process is a function  $Q : \mathbb{R} \to \mathbb{R}$ such that, defining  $X_j = \left| j\Delta - \frac{\Delta}{2}, j\Delta + \frac{\Delta}{2} \right|$ , can be obtained

$$Q(x) = j\Delta \quad \text{if} \quad x \in X_j. \tag{2.24}$$

for a certain quantization step  $\Delta$ .

**Figure 2.3:** Input-Output relation of a quantization process Q(x), of step  $\Delta$ .

Suppose to model the input signal as a RV x, the application of Q on it produces two additional RVs:

The RV that model the quantized value:  $\omega = Q(x)$ . Its characterization is based on the fact that, all the values x that fall in the interval  $X_j$  are associated to  $j\Delta$ .

$$f_{\omega}(z) = \sum_{j=-\infty}^{\infty} \delta(z - j\Delta) \int_{X_j} f_x(y) \, \mathrm{d}y$$

$$= \sum_{j=-\infty}^{\infty} \delta(z - j\Delta) \left[ F_x \left( j\Delta + \frac{\Delta}{2} \right) - F_x \left( j\Delta - \frac{\Delta}{2} \right) \right]. \tag{2.25}$$

The RV that model the error of quantization:  $e = x - \omega$ . Its characterization is much important with respect to Eq. 2.25, because after the quantization process, the system conserve  $\omega$  and ignores e. Thus a statistical model for e is necessary to determine and guarantee the margins of error of the system. There are some assumption that can be made about e:

- 1. *e* is uniformly distributed in the interval  $\left[-\frac{\Delta}{2}, \frac{\Delta}{2}\right]$ ;

- 2. two errors measured in different time intervals, defined as  $e_1$  and  $e_2$ , are at least uncorrelated and, in the best case, independent;

- 3. e and x are uncorrelated and, in the best case, independent.

There are theorems able to verify these conditions the Moment Generating Function (MGF), see Eq. 2.20, of the input RV x. The first one permits to verify the uniform distribution of the quantization error in the interval  $\left[-\frac{\Delta}{2}, \frac{\Delta}{2}\right]$  (cond 1.):

**Theorem 2.7.** If e = x - Q(x) then, e is uniformly distributed in  $\left[-\frac{\Delta}{2}, \frac{\Delta}{2}\right]$  iff

$$\psi_x\left(\frac{k}{\Delta}\right) = 0$$

for all  $k \neq 0$ .

This theorem can be interpreted remembering that  $\psi_x(z) = \mathcal{F}[f_x](-\omega)$ . The PDF of x is a real function.

To verify that two uncorrelated errors of quantization,  $e_0$  and  $e_1$ , are independent (cond 2.) it is valid

**Theorem 2.8.** If  $e_0 = x_0 - Q(x_0)$  and  $e_1 = x_1 - Q(x_1)$  are two quantization errors uniformly distributed in  $\left[-\frac{\Delta}{2}, \frac{\Delta}{2}\right]$ , then they are independent iff

$$\psi_{x_0,x_1}\left(\frac{k_0}{\Delta},\frac{k_1}{\Delta}\right) = 0$$

for each couple  $(k_0, k_1) \neq (0, 0)$ .

There is also a theorem for evaluate the correlation between the input RV and the error of quantization (cond 3.):

**Theorem 2.9.** The input RV x and the error of quantization e, uniformly distributed in  $\left[-\frac{\Delta}{2}, \frac{\Delta}{2}\right]$ , are uncorrelated if

$$\frac{\mathrm{d}}{\mathrm{d}y}\,\psi_x\left(\frac{j}{\Delta}\right) = 0$$

for all  $j \neq 0$ .

## 2.5 Stochastic Process (SP)

A Stochastic Process (SP) is any process that contains some randomness and information which a user wants to extract. It is a fundamental abstraction because it permits to introduce the concept of *time* as follows. Take a SP and extract from it a number of *profiles* at precise time intervals, also called *realizations* of the SP. Then the SP's realizations can be seen as a vector of RVs, namely a *random vector* and each sample is a function (discrete or continuous depending on the initial hypothesis) and can be modeled as a RV, thus all formulas introduced before are usable, such as in Tab. 2.1. These collection of RVs permits to model a SP.

A SP can involve both continuous-time (c-t) and discrete-time (d-t) RVs. In this work the latter will be used more often. Furthermore its realization can assume  $\mathbb{C}$  or  $\mathbb{R}$  values, notice that all the theory developed for complex values can be reduced simply for real values RVs, so it is preferred in this work because it is more general.

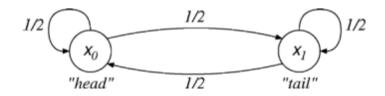

Remember the ideal RNG showed in sec. 1.1 ? In statistical terms it can be described with a discrete-time stochastic process, formed by a sequence of *independent* and uniformly distributed (IID) random variables, distributed in the set  $\{0, 1\}$ , with probability p = 0.5. This stochastic process is very common in literature and is known as **Bernoulli process**.

#### 2.5.1 SP Characterization

Generally exists three ways to model a SP:

- **1. Joint PDF characterization.** The first type of char is the most complete, but requires a huge amount of data. Fixing *n* time instants  $t_0 < t_1 < ... < t_{n-1}$ , it is possible to get a collection of *n* profiles  $x(t_0), x(t_1), ..., x(t_{n-1})$  from the SP, then find its joint PDF of order *n*:  $f_{x(t_0)x(t_1)...x(t_{n-1})}(y_0, y_{1,1}, ..., y_{n-1})$ . For  $n \to \infty$ , the joint PDS provides any information about the SP but is evidently infeasible in practice; it is usual to steak to *second* order joint PDS characterization.

- **2.** Autocorrelation-Autocovariance function characterization. The second type of characterization involves *auto*-function, that in statistical terms means to

evaluate a RV and its evolution in time. To clarify this concept take the covariance between two discrete-time RVs, as showed in Eq. 2.21,  $x_0 = x_0 [0]$ and  $x_1 = x_0 [1]$ , so  $\gamma_{x_0x_1}$  is the covariance of  $x_0$  against a time-shifted version of itself, namely the auto-covariance of  $x_0$ . With this notion in mind, a SP can be characterized from the auto-covariance and auto-correlation functions of its realizations in the time interval  $t_0 < t_1 < ... < t_{n-1}$ :

$$C_x(t_0, t_1, \dots, t_{n-1}) = \mathbb{E}\left[x^*(t_0)x(t_1)x^*(t_2)\dots x(t_{n-1})\right].$$

(2.26)

auto-correlation is the cross-correlation of a RV with itself in time

$$K_{x}(t_{0}, t_{1}, ..., t_{n-1}) = \mathbb{E}\left[\left(x(t_{0}) - m_{x(t_{0})}\right)^{*}\left(x(t_{1}) - m_{x(t_{1})}\right) ... \left(x(t_{n-1}) - m_{x(t_{n-1})}\right)\right].$$

(2.27)

As before, it is impossible the extend to infinity the order of characterization so it is sufficient to limit the evaluation at the  $2^{ND}$  order, n = 2, to extract information about the *energy* of the SP from the knowledge of Eq. 2.26 or Eq. 2.27 that are both *positive definite* functions(matrix). In the Fourier domain, this fact translates into a real, positive power density spectrum.

**3. Projections characterization.** The third type of characterization is the most powerful. Suppose to fix an interval of observation  $\left[-\frac{T}{2}, \frac{T}{2}\right]$ , given a SP x it is possible to define all of its realization as *vector space* v. It is now possible to project (scalar product) the realizations on some function  $\varphi_j$ , obtaining the **projection**  $\rho_j:\rho_j = \langle \varphi_j, x \rangle$ . The parameter j dictates the order of aproximation. It is possible to reverse the formula  $\sum_j \rho_j \varphi_j$ . The set of  $\varphi_j$  have to be made of *orthogonal* function, such that  $\langle \varphi_j, \varphi_k \rangle = 0$  for each  $j \neq k$ , and *orthonormal* functions, such that  $\langle \varphi_j, \varphi_k \rangle = 1$  for j = k, to assure that they are linear independent functions. To obtain the maximum information with the minimum value of j, it is sufficient that all the projections are uncovariated.

### 2.5.2 SP Stationarity

Another basic concept is *stationarity*. Imagine to model and design a system, the prototype must work not only during the testing phase but also during operation time, that is much and much longer than testing phase. Considering this system as a SP is possible to use this theorem with many *degree* or *order* of stationarity:

**Definition 2.12.** A SP is *m*-order stationary, with  $m = 1, 2, 3, ..\infty$ , if  $\forall m$  and  $\forall t_0, t_1, ..., t_{m-1}$ , its joint PDF it is:

$$f_{x(t_0)\dots x(t_{m-1})} = f_{x(t_0 + \Delta t)\dots x(t_{m-1} + \Delta t)}.$$

(2.28)

and Eq. 2.28 is valid  $\forall \Delta t \in \mathbb{R}$  for continuous-time SP and  $\forall \Delta t \in \mathbb{Z}$  for discrete-time SP.

This means that, all the statistical features of the SP are invariant with respect to any translation in time. Claim to reach infinite order stationarity is absurd, a second order (m = 2) stationarity is a good tradeoff.

**Definition 2.13.** A SP is said to be *cycle-stationary* with period T if, for each integer m and time interval  $t_0, t_1, ..., t_{m-1}$

$$f_{x(t_0)\dots x(t_{m-1})} = f_{x(t_0+k_1)\dots x(t_{m-1}+k_m)},$$

(2.29)

for each integer k .

## 2.6 Gaussianity

#### 2.6.1 Jointly Gaussian Vector (JGV)

The Gaussian theory it is a fundamental part security engineering because it permits to model a lot of situations and it has a set of strong properties that simplify a lot the work. Notice that any Gaussian RV can be completely characterized in terms of its mean and variance.

**Definition 2.14.** Given a set of *n* real RVs that forms what is called a **random** vector,  $x = x_0, x_1, ..., x_{n-1}$ .

This collection of RVs is a Jointly Gaussian Vector (JGV) if:

$$f_x(y) = \frac{1}{2\pi^{n/2} \det(K_x)} e^{-\frac{1}{2}(y-\mathbf{m}_x)^t K_x^{-1}(y-\mathbf{m}_x)}.$$

(2.30)

Notice that this definition can be extended also to complex RVs x = a + ib where  $a = Re \{x\}$  and  $b = Imm \{x\}$ , adding the following condition

$$K_{aa} = K_{bb}$$

$$K_{ab} = -K_{ba}$$

Eq. 2.30 is the same with transposition operator t substituted by the conjugate = transpose operator +.

The square auto-correlation matrix of a real discrete-value JGV satisfy certain properties:

- $K_x$  is symmetric  $K_x = K_x^t$ .<sup>3</sup>

- $\blacktriangleright$   $K_x$  is a positive semi-definite matrix

- $K_x$  is non-singular; so it is invertible and  $det(K_x) \neq 0$ .

3

<sup>•</sup> In case of a complex JGV the auto-correlation matrix is *hermitian*

Another important Gaussian property regards the MGF, recall Eq. 2.20:

**Theorem 2.10.** Given a JGV  $x = x_0, x_1, ..., x_{n-1}$  and its associated MGF  $\psi_x$ . It valid the following relation:

$$\mathcal{F}^{-1}\left[f_x\right](w) = \psi_x(w).$$

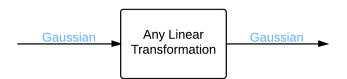

Thanks to this particular theorem it is possible to say that *any* linear transformation that take as input something that is Gaussian returns as output something Gaussian.

Figure 2.4: Linear transformation of a Gaussian quantity.

Given an input JGV x with mean  $m_x$  and auto-covariance matrix  $K_x$  and a linear transformation A that produces a Gaussian JGV output w; then there is a linear relation between the mean/auto-covariance of the input and the output:

$$\mathbf{m}_w = \mathbf{A}\mathbf{m}_x.$$

$$K_w = \mathbf{A} K_x \mathbf{A}^t$$

Given a JGV it is possible to see if it is formed by independent RVs only looking to its  $K_x$ .

**Theorem 2.11.** Given a JGV  $x = x_0, x_1, ..., x_{n-1}$ , if for each couple j, k with  $j \neq k$ , the expectation  $E\left[\left(x_j - m_{x_j}\right)^t (x_k - m_{x_k})\right] = 0$  then  $x_0, x_1, ..., x_{n-1}$  are independent RVs

#### 2.6.2 Additive White Gaussian Noise SP (AWGN)

It is important to mention at least one of the most important type of *discrete-value* real SP.

**Definition 2.15.** A SP can be defined as **Gaussian Stochastic Process (GSP)** if:

$p = \langle \varphi, x \rangle$

is a Gaussian RV for each  $\varphi \in L^2$

So to characterize a GSP it is sufficient to use a *projection* model and choose a set of orthonormal basis  $\varphi$  and know the statistics of the projections. There are at least three fundamental properties of a GSP:

- 1. Any sample  $x[t_n]$  of a GSP is a Gaussian RV, and any linear combination of a finite number of sample is a JGV.

- 2. A GSP is completely characterize by the mean and the auto-covariance of its projections.

- 3. Any linear filtering h of an input GSP produces a GSP output.

There is a particular type of GSP called *White Noise GSP* or simply *White Gaussian Noise (WGN)*. It is often incorrectly assumed that Gaussian noise is necessarily white noise, yet neither property implies the other. Gaussianity refers to the probability distribution with respect to the value, in this context the probability of the signal reaching an amplitude, while the term *white* refers to the way the signal power is distributed over time or among frequencies. We can therefore find Gaussian white noise, but also Poisson, Cauchy, etc. white noises. Thus, the two words "Gaussian" and "White" are often both specified in mathematical models of systems.

**Definition 2.16.** A SP x is called **White Gaussian Noise SP (WGN SP)** if for each  $\varphi \in L^2$  any projection  $p = \langle \varphi, x \rangle$  is a Gaussian RV with mean  $m_p$  and variance  $\sigma_p^2$ .

A discrete-value second order projection characterization of a WGN SP is a good approximation of many real-world situations such has disturbance during a measurement. In this case it is allowed to use the word *additive* because the noise can be treated as an additive term that sums to the useful one (linear relation). Also notice that:

$$E[p_0 p_1] = \frac{N_0}{2} \langle \varphi_0, \varphi_1 \rangle = 0.$$

(2.31)

$$K_p = \begin{array}{cc} \sigma_{p_0}^2 & 0\\ 0 & \sigma_{p_1}^2 \end{array}$$

(2.32)

So with this characterization it is impossible to linearly predict any terms because the cross-correlation between different projections it is always 0. In fact the terms *White* is used because the Power Density Spectrum (PDS) of a WGN SP, that is simply the Fourier transform of the auto-correlation function, is **flat**, so there are no dominant frequency component that carrier higher amount of energy.

# 2.7 Entropy

The most important metric to analyze and test a RNG is **entropy**. Its definition is taken from *Information Theory* field, and it is abstract and different from the definition of entropy in thermodynamics sense. It is a real number between zero and one, that gives a measure of how random a particular process is. There are several way to measure it, historically the first definition is *Shannon entropy* that comes from by CLAUDE SHANNON[31]:

$$H_i = -\sum_{i=i}^{n} p_i log_2\left(p_i\right) \tag{2.33}$$

$H_i$  quantify how much bits of information can be compressed in a *loss-less* bit sequence, in our terms this translates in how much randomness is present in a bit sequence. One perfect coin toss contains one bit of entropy (or one bit of information because of no redundancy). By using a base-2 logarithm the entropy is measured in bit. In the formulas  $p_i$  is the probability of the process of being in the *i*th of *n* possible states, or returning the *i*th of *n* possible outputs. In Fig. 2.5 there is an example of Shannon's entropy computation<sup>4</sup>:

#### Your string is: 0111101010100101001

Alphabet of symbols in the string:0 1 Frequencies of alphabet symbols:

0.526 -> 1

Shannon entropy can be calculated as follow:

$H(X) = -[(0.474log_20.474)+(0.526log_20.526)]$  H(X) = -[(-0.511)+(-0.487)] H(X) = -[-0.998]H(X) = 0.998

Figure 2.5: Shannon entropy computation.

To better understand and also extend the last definition is often useful talk in term of *entropy rate* or *entropy per symbol*, that is applied to bit sequence that

<sup>&</sup>lt;sup>4</sup>Free Shannon entropy calculator/tutorial http://www.shannonentropy.netmark.pl/

encode a specific alphabet formed by symbols. As an example, consider a source that produces the sequence ABABABAB... If the symbol's length is equal to one, the entropy rate 1 bit per character but, if the symbols are formed by two letter the entropy rate is 0 bit per character, because the same symbol is repeating over time. These simple example underlines how much randomness is subject to the boundary condition.

There is also a lower bound quantity, namely *min-entropy*:

$$H_{\infty} = \min_{i=i}^{n} \left( -\log_2\left(p_i\right) \right) \tag{2.34}$$

that measures the probability that an attacker can guess the state with a single guess. Notice that:

$$H_{\infty} \le H_i \tag{2.35}$$

the min-entropy of a process is always less or equal to its Shannon entropy.

As an example, in the case of a RNG that produces a k-bit binary result, e.g. 010101 for k = 6,  $p_i$  is the probability that an output will equal *i*, where  $0 \le i < 2^k$ . Thus a *perfect* binary RNG has  $p_i = 2^{-k}$ , so Eq. 2.33 and Eq. 2.34 are both equal to k bits, and all possible outcomes are equally likely (IID outputs). The information present in the output cannot, on average, be represented in a sequence shorter than k bits, and an attacker cannot guess the output with probability greater than  $2^{-k}$ . A random number generator for cryptographic applications should appear to relative computationally-bounded adversaries to be close as possible to a perfect RNG, so for a good analysis result a target RNG, at least in principle, shall not be distinguishable from a perfect RNG that is an useful ideal abstraction.

### 2.8 Hamming Distance

The first error correction code was used in 1950 to detect errors in telephone central offices to provide a better Quality of Service (QoS) in the American Telephone and Telegraph Company (AT&T) and it was used also for digital computer applications by RICHARD HAMMING [9]. While, at that time, *error detecting* codes, such as 20ut-of-3 or 30ut-of-7 code, and *self-checking* circuit were still available, error *correction* had represented a big step forward in computer science.

As first hypothesis each code *symbol* or *word* is represented in the *binary* form, by a sequence of 0's and 1's. All code used in this subsection are defined as *systematic*, that are codes whose

- 1. Symbol length are all equal, they are formed by n = k + m binary digits where

- a) n total symbol's bit,

- b) m information bits,

- c) k error detection and correction bits.

- 2. The position checked are independent of the information contained in the symbol,

- 3. The checks are independent of each other,

- 4. Use *Parity check* bit.

Hypothesis 1. produces **redundancy**  $\mathbf{R}$  in the code, defined as the ratio of total symbol's bit and the information bits.

$$R = n/m \tag{2.36}$$

This serves to measure the *efficiency* of the code, because on one side R can lower the effective channel capacity for sending information plus the need of extra hardware equipment but on the other side, is impossible to detect and correct an errors without introducing redundancy in the code.

To define an error correcting code first it is necessary to pass from an error detecting one because any d error correcting code is also an d error detecting code, obviously the inverse is not true. To check a symbol the most common method used is the *parity check*. As an example consider the *even(odd)* parity check: take a symbol of n bits, put m = n - 1 bits of information, and the last either a 0 or a 1 so that the symbol has an *even(odd)* number if 1's. This is clearly a single error detecting code, since any single error in a symbol would leave an *odd(even)* number of bits. The redundancy of this code is:

$$R = \frac{n}{n-1} = 1 + \frac{1}{n-1}$$

Increasing n, the probability of at least one error in a symbol increase; and the risk of a *double* error, which would pass undetected, also increase. Furthermore, a parity check need not always involve all positions of the symbol but may be a check over *selected* position.

To extend and control the power of error correcting and detecting code it is useful to introduce a *geometrical* model, that consists in identifying the various sequences of 0's and 1's, which are the symbol (word) of a code, with vertices of a unit *n*-dimensional cube. The code *points*, each one of *n* bits, are labeled as x,y,z,... and they form a subset of the set of all vertices of the cube. Thus the space is formed by  $2^n$  points and can be introduced a (Hamming) distance D(x,y), called also as a *metric*. By definition, a single error in a code point changes one coordinate, two errors two coordinates, and in general *d* errors produce a difference in *d* coordinates. So, coming back to the unit cube, the minimum number of edges which must be traversed in going from x to y, represent the distance D(x,y) between the two code points, or in other terms the number or error(s) between the two code symbols, see Fig. 2.6.

Figure 2.6: 0100 $\rightarrow$ 1001 has distance 3 (red path); 0110 $\rightarrow$ 1110 has distance 1 (blue path).

This distance function satisfies the usual three conditions for a metric, namely:

- 1. D(x,y) = 0 if and only if x = y

- 2. D(x,y) = D(y,x) > 0 if  $x \neq y$

- 3.  $D(z, y) + D(y, z) \ge D(x, z)$  (triangle inequality)

To continue the geometric language, a sphere of radius r about a point x, is defined as all points which are at a distance r from the point x. As an example consider a code with n = 3, and four code points: 001,010,100,111. Each symbol may be chosen as the *center* of a sphere of radius r = 2, and the other three symbol lies on the sphere's surface or in simple words the minimum distance between all code words is two. Thus it follows that any single error will carry a code point to a meaningless symbol. This in turn means that any single error is detectable with this code. Additionally, if the minimum distance between code points is three, then any single error will leave the point nearer to the correct code point than to any other code points, and this means that any single error will be correctable. Go deep with this theory permits to link the minimum distance of code points with code's features, as show in Tab. 2.2

| $\mathbf{D_{min}}(\mathbf{x},\mathbf{y})$ | $ \mathbf{D}_{\min}(\mathbf{x}, \mathbf{y}) $ Code Features |  |  |  |

|-------------------------------------------|-------------------------------------------------------------|--|--|--|

| 1                                         | Uniqueness                                                  |  |  |  |

| 2                                         | Single Error Detection                                      |  |  |  |

| 3                                         | Single Error Correction                                     |  |  |  |

| 4                                         | Single Error Correction + Double Error Detection            |  |  |  |

| 5 Double Error Correction                 |                                                             |  |  |  |

|                                           | Etc.                                                        |  |  |  |

| Table 2.2:         Minimum | distance $D_{min}$ | (x,y) of co | ode points vs | Code's features. |

|----------------------------|--------------------|-------------|---------------|------------------|

|----------------------------|--------------------|-------------|---------------|------------------|

All the distances between code points must equal or exceed the minimum distance listed. Thus the problem of finding suitable codes is the same as that of finding subsets of points in the space, which maintain *at least* the minimum distance condition.

It should be noted that, at a given minimum distance, some of the correctability may be exchanged for more detectability; e.g., a subset of code points with  $D_{min}(x, y) = 5$  can be used in different manners:

- ▶ double error correcting code, thus also double error correction;

- ▶ single error correction + triple error detection;

- ▶ quadruple error detection, without correction.

Two codes are said to be *equivalent* to each other if, by a finite number of the following operation, one can be transformed into the other:

- 1. The interchange of any two positions in the code symbols;

- 2. The complementing of the values in any position of the code symbols.

This definition is very useful because it permits to study a class of codes to the study of typical members of each *equivalence class*. Furthermore, in terms of the geometric representation, equivalence transformations amount to *rotations* (interchange) and *reflections* (complementing) of the unit cube.

The last useful thing to know regards *minimum redundancy* and can be summarized by a powerful general theorem, that is valid for systematic code, where points means number of code symbols and dimensions means symbol's bit length:

**Theorem 2.12.** To any minimum redundancy code of N points in n-1 dimensions and having minimum distance of 2k-1, there corresponds a minimum redundancy code of N points in n dimensions having a minimum distance of 2k, and conversely

This theorem permits to construct min redundancy code (N is fixed) of any minimum distance starting from the simplest one k=1 .

Hamming distance is used in several disciplines including information theory, coding theory, and cryptography. In this work Hamming weight analysis of bits is used as a metric of RNG performance in sec. 4.2.

# 2.9 Limit Behavior of RVs

Try to find for a particular series of RVs  $x_0, x_1, ..., x_{n-1}$  that can be approximated by RV x. This study starts from the relation of the PDFs of the series and the PDF of the limit RV. The first approach can be with a punctual convergence for their associated PDFs, but it is not too much. A second approach can be with uniform convergence for their PDFs, but this is a too stringent condition. It is needed something in between:

**Definition 2.17.** Given a series of functions  $f_k$  I can define a **weak** convergence to the function f as:

$$f_k \to^w f$$

if for each function  $g \int f_k g = \int f g$ .

There is a specialized Theorems for weak convergence of RVs series.

**Theorem 2.13.** Lyapunov. Given a series of RVs  $x_0, x_1, ..., x_{n-1}$  with PDFs  $f_k$  and CDF  $F_k$ , given a single RV x with PDF f and CDF F $f_k \rightarrow^w f'$  iff  $F_k \rightarrow F$ . and  $f_k \rightarrow^w f$  if  $\psi_{x_k} \rightarrow \psi_x$ . Thus  $x_k \rightarrow x$ .

The second is much more famous with respect to the Lyapunov theorem

**Theorem 2.14.** Central Limit Theorem (CLT). Given a series  $\mathbb{R}$  independent RVs  $x_0, x_1, ..., x_{n-1}$  with means  $m_{x_j} = 0$  and variance  $\sigma_{x_j}^2$ . It is possible to define  $S_w = \sum_{j=0}^{k-1} x_j$  and  $w' = \frac{1}{k} \sum_{j=0}^{k-1} x_j$  and  $w'' = \frac{1}{\sqrt{k}} \sum_{j=0}^{k-1} x_j$ .

- 1. If, for each  $j,\ lim_{k\to\infty}\frac{1}{k^2}\sum_{j=0}^{k-1}\mu_{x_j}^2=0$  then  $f_{w'}\to^w\delta$  .

- 2. If, for each j,  $\lim_{k\to\infty} \frac{1}{k^{3/2}} \sum_{j=0}^{k-1} \mu_{x_j}^3 = 0$  and  $\lim_{k\to\infty} \frac{1}{k} \sum_{j=0}^{k-1} \sigma_{x_j}^2 = \sigma^2 < \infty$ . then

$$f_{w''} \to^w \frac{1}{\sqrt{2\pi\sigma}} e^{-\frac{1}{2}\frac{z^2}{\sigma^2}}.$$

So the PDF normalized sum, that is not the joint PDF of the RVs, tends to a Gaussian PDF with known mean and variance.

**Theorem 2.15.** *de Moivre-Laplace.* From CLT can be deduced a special case stating that: given a binomial SP (Bernoulli) of n samples where the trials are independent and the probability of success is p and probability of insuccess q = 1 - p for each. If n is very large the SP can be asymptotically approximated by a Gaussian RV with mean equal to np and std deviation equal to  $\sqrt{npq}$ .

$$\binom{n}{k} p^k q^{n-k} \simeq \frac{1}{\sqrt{2\pi n p q}} e^{-(k-np)^2/(2npq)}, \quad p+q=1, \ p>0, \ q>0.$$

(2.37)

# 2.10 Pearson's Chi-Squared test (P $\chi^2$ t)

Pearson's  $\chi^2$  statistical test is the best-know of several chi-squared test, that are statistical procedures whose results are evaluated by reference to an ideal **Chi-Squared PDF** with k degrees of freedom.

**Definition 2.18.** Chi-Squared PDF with k degrees of freedom.

$$\chi^{2}(k) = \frac{1}{2^{\frac{k}{2}}\Gamma(\frac{k}{2})} x^{(\frac{k}{2}-1)} e^{-\frac{x}{2}}.$$

(2.38)

where  $\Gamma(n)$  is the gamma function<sup>5</sup>

$$\Gamma(z) = \int_0^\infty t^{(z-1)} e^{-t} dt.$$

(2.39)

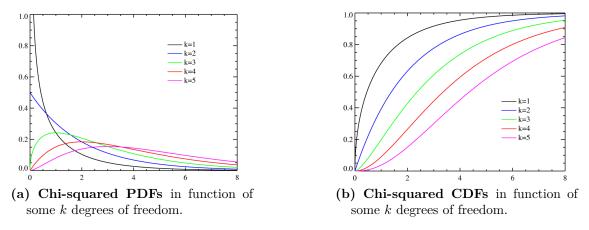

In Fig. 2.7 it is plotted  $\chi^2$  PDFs in function of k:

<sup>&</sup>lt;sup>5</sup>not be confused with *gamma PDF*. gamma PDF is a generalization of the chi-squared PDF, or in other term chi-squared PDF is a special case of gamma PDF

**Figure 2.7:**  $\chi^2$  in function of some k degrees of freedom.

Notice that  $\chi^2(k)$  is the distribution of a sum of the squares of k independent Gaussian RVs.<sup>6</sup>

Generally  $P\chi^2 t$  tests a **null hypothesis** (H<sub>0</sub>) on an "observed event". In the specific it tests whether outcome frequencies (e.g., number of logical '0' vs logical '1' in a bit sequence follow a specified distribution, also called *goodness-of-fit* testing. This fact is coded in the similarity between the sampled PDF and an ideal chi-squared PDF. The level of similarity reject or not the null hypothesis. Notice that exists also the *alternative hypothesis* associated to the null one, defined as H<sub>a</sub>.

**Theorem 2.16.** *Pearson's chi-squared test.* Given a null hypothesis  $H_0$  and n binomially samples to test it (goodness of fit test) it is possible to compute an observed statistic on  $it:\chi_{obs}^2$ . If n is large enough, the comparison between  $\chi_{obs}^2$  and a ideal chi-squared statistics  $\chi^2$  with k degrees of freedom provides a measure of accuracy of  $H_0$  over n samples (*P*-value).

The application of this kind of test in the filed of TRNG will be extensively explained in sec. 5.2.

$<sup>^6\</sup>mathrm{called}$  also normal or standard RVs for their huge use in statistics

# **3** Architecture & Design of RNG

## 3.1 Analog Chaotic ADC

The first TRNG proposed is a mixed non-linear circuit based on an *analog* ES circuit. The implementation refers to [25, 6, 26].

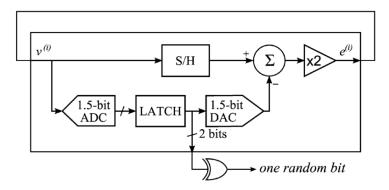

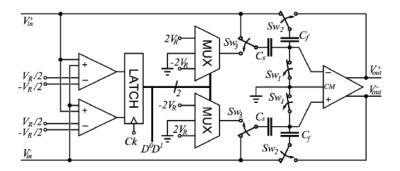

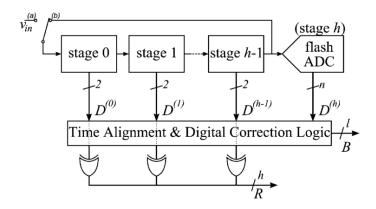

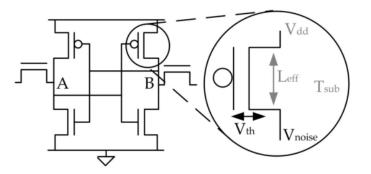

#### 3.1.1 Pipeline ADC Converter

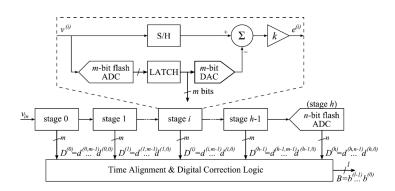

The implementation is based on a pipeline ADC converter. The h+1 stage converter shown in Fig. 3.1, provides a representation of an input variable  $v_{in}$  defined in a interval X into a *l*-bits numerical notation. It's not necessary that all stages are identical but in this example the first h stages are m-bit ADCs and they are identical, while the last one, a n-bit ADC, has a simpler structure because it's not necessary the computation of its conversion error.

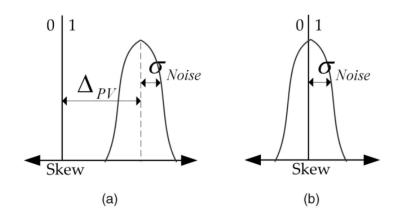

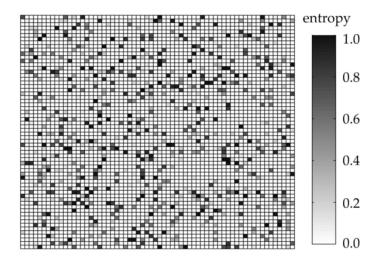

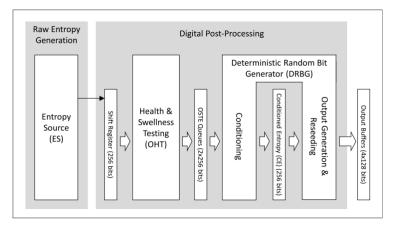

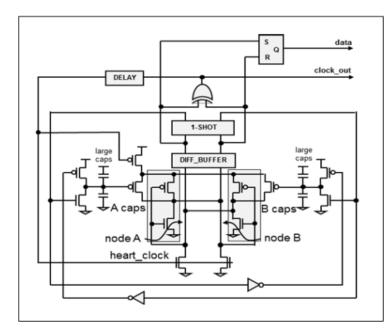

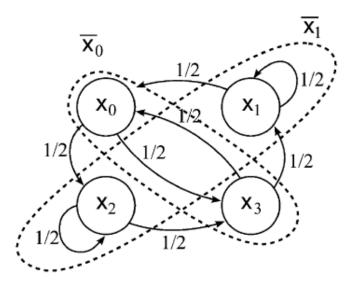

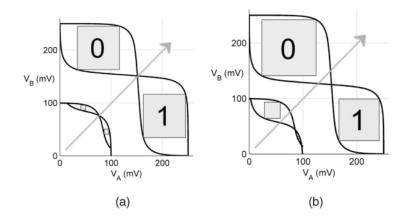

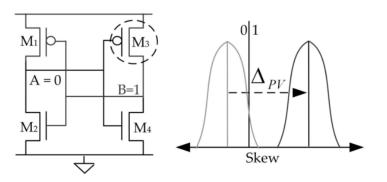

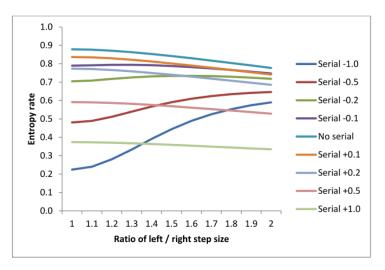

Figure 3.1: Basic Structure of a Pipeline ADC.